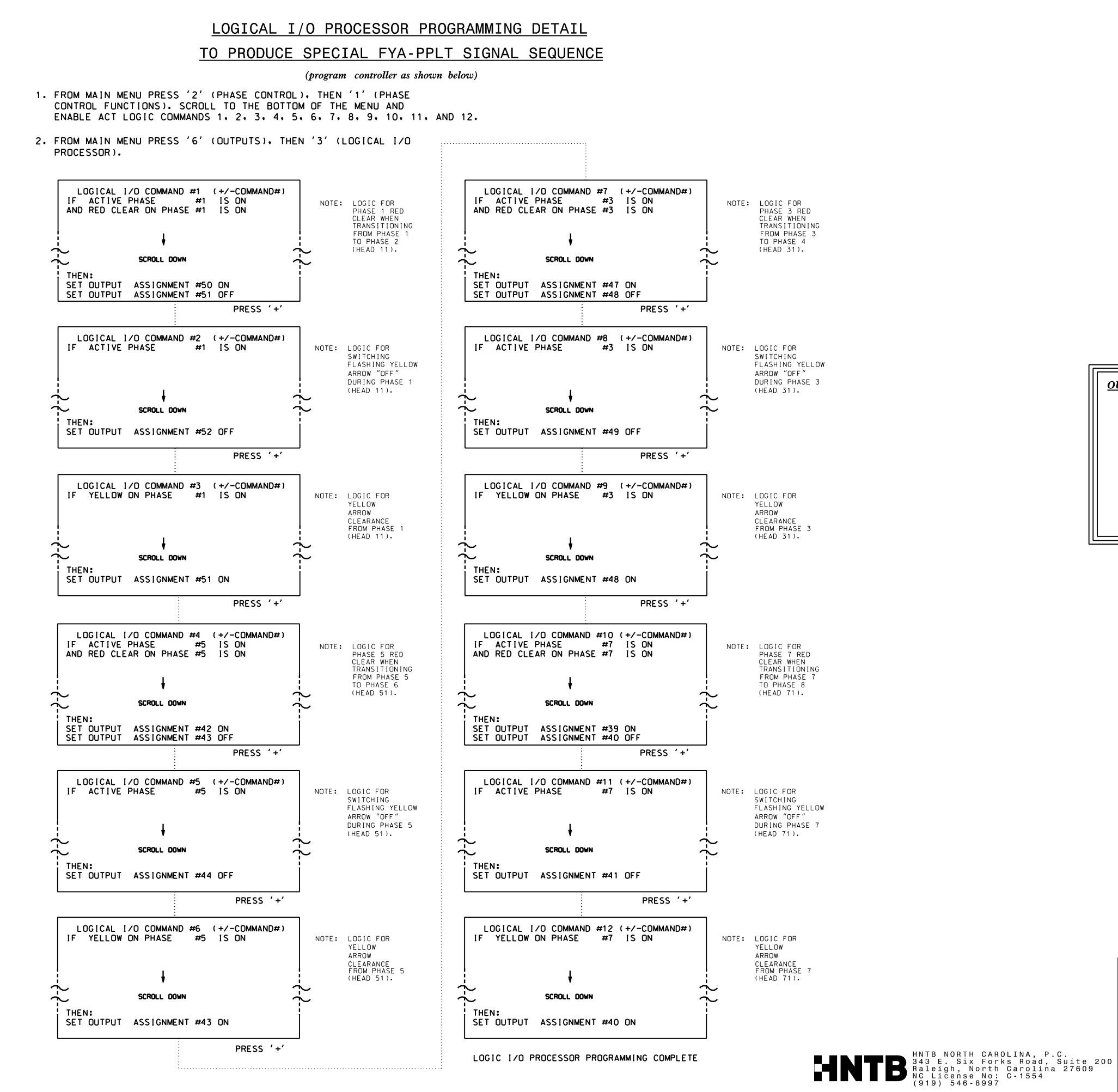

| <u>OUTPUT REFERENCE SCHEDULE</u> |  |  |  |

|----------------------------------|--|--|--|

| USE TO INTERPRET LOGIC PROCESSOR |  |  |  |

| OUTPUT 39 = Overlap D Red        |  |  |  |

| -                                |  |  |  |

| OUTPUT 40 = Overlap D Yellow     |  |  |  |

| OUTPUT 41 = Overlap D Green      |  |  |  |

| OUTPUT 42 = Overlap C Red        |  |  |  |

| OUTPUT 43 = Overlap C Yellow     |  |  |  |

| OUTPUT 44 = Overlap C Green      |  |  |  |

| OUTPUT 47 = Overlop B Red        |  |  |  |

| OUTPUT 48 = Overlap B Yellow     |  |  |  |

| OUTPUT 49 = Overlap B Green      |  |  |  |

| OUTPUT 50 = Overlap A Red        |  |  |  |

| OUTPUT 51 = Overlap A Yellow     |  |  |  |

| OUTPUT 52 = Overlap A Green      |  |  |  |

|                                  |  |  |  |

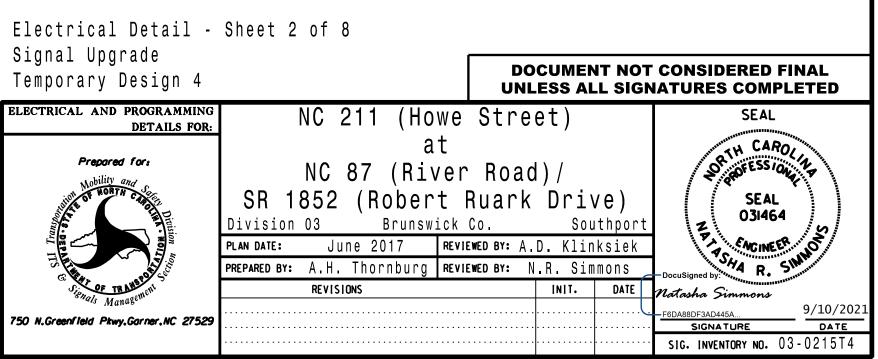

| PROJECT REFERENCE NO. | SHEET NO. |      |

|-----------------------|-----------|------|

| R-5021                | Sig.      | 42.2 |

THIS ELECTRICAL DETAIL IS FOR THE SIGNAL DESIGN: 03-0215T4 DESIGNED: June 2017 SEALED: 9/10/2021 REVISED: N/A