**←** NOTICE

GREEN

FLASH

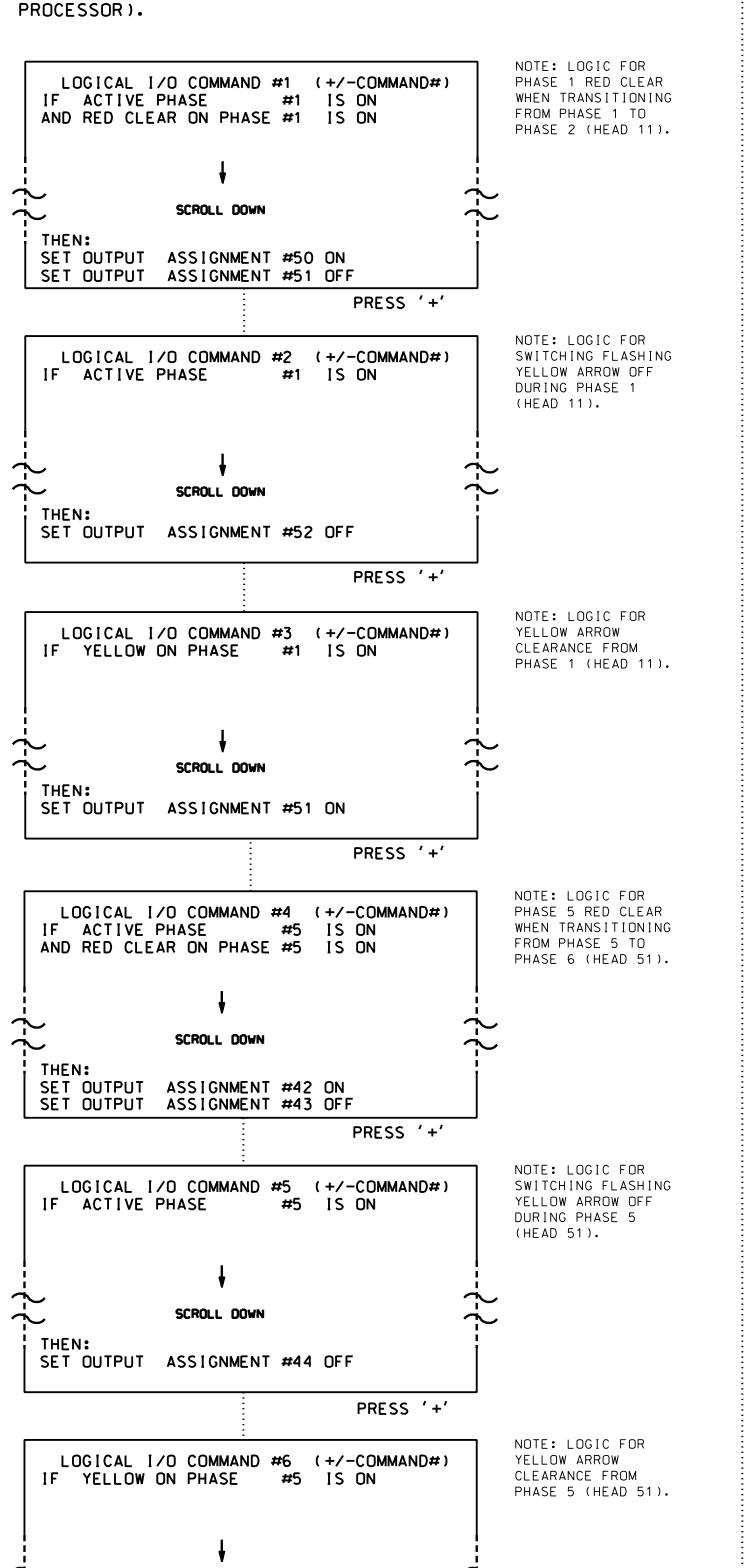

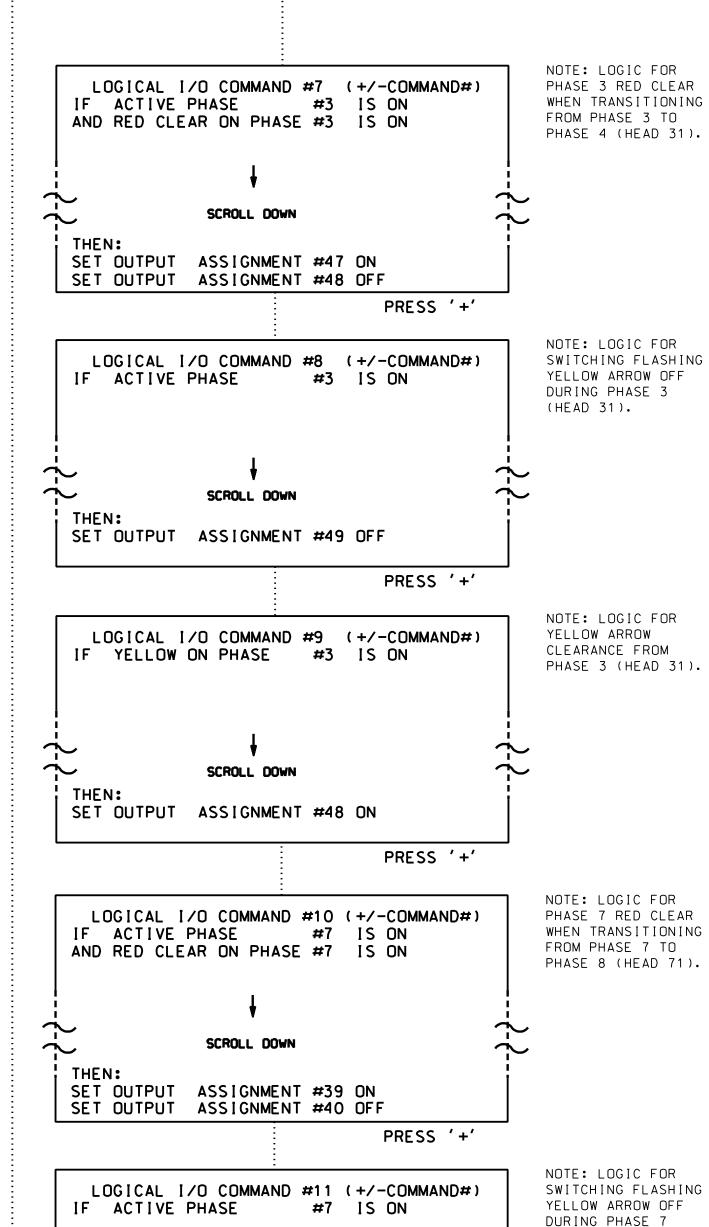

#### LOGICAL I/O PROCESSOR PROGRAMMING DETAIL

### TO PRODUCE SPECIAL FYA-PPLT SIGNAL SEQUENCE

(program controller as shown below)

1. FROM MAIN MENU PRESS '2' (PHASE CONTROL), THEN '1' (PHASE CONTROL FUNCTIONS). SCROLL TO THE BOTTOM OF THE MENU AND ENABLE ACT LOGIC COMMANDS 1, 2, 3, 4, 5, 6, 7, 8, 9, 10, 11, AND 12.

2. FROM MAIN MENU PRESS '6' (OUTPUTS), THEN '3' (LOGICAL I/O

SCROLL DOWN

PRESS '+'

SET OUTPUT ASSIGNMENT #43 ON

SCROLL DOWN

LOGICAL I/O COMMAND #12 (+/-COMMAND#)

SET OUTPUT ASSIGNMENT #41 OFF

IF YELLOW ON PHASE #7 IS ON

SCROLL DOWN

LOGIC I/O PROCESSOR PROGRAMMING COMPLETE

SET OUTPUT ASSIGNMENT #40 ON

(HEAD 71).

NOTE: LOGIC FOR

CLEARANCE FROM

PHASE 7 (HEAD 71).

YELLOW ARROW

PRESS '+'

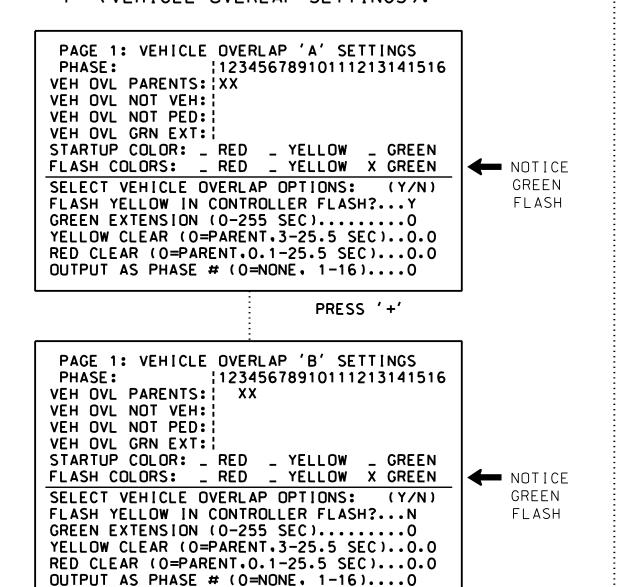

# OVERLAP PROGRAMMING DETAIL

(program controller as shown below)

FROM MAIN MENU PRESS '8' (OVERLAPS). THEN '1' (VEHICLE OVERLAP SETTINGS).

PAGE 1: VEHICLE OVERLAP 'C' SETTINGS 12345678910111213141516 VEH OVL PARENTS: ; VEH OVL NOT VEH: VEH OVL NOT PED: VEH OVL GRN EXT: : STARTUP COLOR: \_ RED \_ YELLOW \_ GREEN FLASH COLORS: \_ RED \_ YELLOW X GREEN **→** NOTICE SELECT VEHICLE OVERLAP OPTIONS: (Y/N) GREEN FLASH YELLOW IN CONTROLLER FLASH?...Y FLASH GREEN EXTENSION (0-255 SEC)..... YELLOW CLEAR (O=PARENT.3-25.5 SEC)..0.0 RED CLEAR (0=PARENT.0.1-25.5 SEC)...0.0 OUTPUT AS PHASE # (0=NONE, 1-16)....0 PRESS '+'

PAGE 1: VEHICLE OVERLAP 'D' SETTINGS 12345678910111213141516 VEH OVL PARENTS:! VEH OVL NOT VEH: : VEH OVL NOT PED: VEH OVL GRN EXT: : STARTUP COLOR: \_ RED \_ YELLOW \_ GREEN FLASH COLORS: \_ RED \_ YELLOW X GREEN SELECT VEHICLE OVERLAP OPTIONS: (Y/N) FLASH YELLOW IN CONTROLLER FLASH?...N GREEN EXTENSION (0-255 SEC)...... YELLOW CLEAR (0=PARENT.3-25.5 SEC)..0.0 RED CLEAR (0=PARENT.0.1-25.5 SEC)...0.0 OUTPUT AS PHASE # (0=NONE, 1-16)....0

OVERLAP PROGRAMMING COMPLETE

# FLASHER CIRCUIT MODIFICATION DETAIL

IN ORDER TO INSURE THAT SIGNALS FLASH CONCURRENTLY ON THE SAME APPROACH, MAKE THE FOLLOWING FLASHER CIRCUIT CHANGES:

- 1. ON REAR OF PDA REMOVE WIRE FROM TERM. T2-4 AND TERMINATE ON T2-2.

- 2. ON REAR OF PDA REMOVE WIRE FROM TERM. T2-5 AND TERMINATE ON T2-3.

- 3. REMOVE FLASHER UNIT 2.

PRESS '+'

THE CHANGES LISTED ABOVE TIES ALL PHASES AND OVERLAPS TO FLASHER UNIT 1.

#### **OUTPUT REFERENCE SCHEDULE** USE TO INTERPRET LOGIC PROCESSOR

OUTPUT 39 = Overlap D Red OUTPUT 40 = Overlap D Yellow OUTPUT 41 = Overlap D Green OUTPUT 42 = Overlap C Red OUTPUT 43 = Overlap C Yellow OUTPUT 44 = Overlap C Green OUTPUT 47 = Overlap B Red OUTPUT 48 = Overlap B Yellow OUTPUT 49 = Overlap B Green OUTPUT 50 = Overlap A Red OUTPUT 51 = Overlap A Yellow OUTPUT 52 = Overlap A Green

THIS ELECTRICAL DETAIL IS FOR THE SIGNAL DESIGN: 10-0617T1 DESIGNED: December 2017 SEALED: 04-23-2018 REVISED: N/A

Electrical Detail - Sheet 2 of 2

| Signal Upgrade Temporary Design 1 ELECTRICAL AND PROGRAMMING

**DOCUMENT NOT CONSIDERED FINAL UNLESS ALL SIGNATURES COMPLETED**

DETAILS FOR: Prepared in the Offices of:

SR 2136 (Gilead Road) US 21 (Statesville Road)

Division 10 Mecklenburg Co. December 2017 REVIEWED BY: A.D. Klinksiek PLAN DATE: PREPARED BY: A.H. Thornburg REVIEWED BY: N.R. Simmons

031464 CACINEER

TH CAROL

INIT. DATE SIG. INVENTORY NO. 10-0617

HNTB NORTH CAROLINA, P.C.

343 E. Six Forks Road, Suite 200

Raleigh, North Carolina 27609

NC License No: C-1554

(919) 546-8997

750 N.Greenfield Pkwy, Garner, NC 27529

REVISIONS