### ECONOLITE ASC/3-2070 OVERLAP PROGRAMMING DETAIL

(program controller as shown)

- 1. From Main Menu select 2. CONTROLLER

- 2. From CONTROLLER Submenu select | 2. VEHICLE OVERLAPS

#### OVERLAP A

Select TMG VEH OVLP [A] and 'OTHER/ECONOLITE'

TMG VEH OVLP...[A] TYPE: OTHER/ECONOLITE PHASES 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 LAG GRN 0.0 YEL 0.0 RED 0.0 ADV GRN 0.0

OVERLAP C

Select TMG VEH OVLP [C] and 'PPLT FYA'

TMG VEH OVLP...[C] TYPE: .... PPLT FYA PROTECTED LEFT TURN.... PHASE 5 OPPOSING THROUGH..... PHASE 6 FLASHING ARROW OUTPUT....CH11 ISOLATE DELAY START OF: FYA..O.O CLEARANCE..O.O ACTION PLAN SF BIT DISABLE..... 5 ← NOTICE SF END PROGRAMMING

Toggle Twice

## ECONOLITE ASC/3-2070 ACTION PLAN PROGRAMMING DETAIL

1. From Main Menu select | 5. TIME BASE

2. From TIME BASE Submenu select 2. ACTION PLAN

ACTION PLAN...[ 1] TIMING PLAN..... O SEQUENCE..... 0 VEH DETECTOR PLAN.. 2 DET LOG.....NONE FLASH..... -- RED REST..... NO VEH DET DIAG PLN... O PED DET DIAG PLN..0 DIMMING ENABLE.. NO PRIORITY RETURN, NO PED PR RETURN.. NO QUEUE DELAY.... NO PMT COND DELAY NO PHASE 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 PHASE 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 SPC FCT . . . X . . . (1-8) AUX FCT . . (1-3) 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5

## ECONOLITE ASC/3-2070 VEHICLE DETECTOR SETUP PROGRAMMING DETAIL FOR ALTERNATE PHASING LOOP 5A

(program controller as shown)

# IMPORTANT!

Program detectors per the input file connection and programming chart shown on sheet 1 before proceeding.

- 1. From Main Menu select | 8. UTILITIES |

- 2. From UTILITIES Submenu select | 1. COPY/CLEAR |

- 3. Copy from DETECTOR PLAN "1" to DETECTOR PLAN "2".

COPY / CLEAR UTILITY FROM PHASE TIMING.... > PHASE TIMING.... TIMING PLAN..... > TIMING PLAN..... PH DET OPT PLAN. . > PH DET OPT PLAN. . DETECTOR PLAN... 1 > DETECTOR PLAN... 2 TOGGLE TO SELECT A "FROM" AND A "TO" THEN PRESS ENTER

- 4. From Main Menu select 6. DETECTORS

- 5. From DETECTOR Submenu select | 2. VEHICLE DETECTOR SETUP

- 6. Place cursor in VEH DET PLAN [ ] position and enter "2".

- Place cursor in VEH DETECTOR [ ] position and enter "5".

- Set delay time to "3.0".

VEH DETECTOR [ 5] VEH DET PLAN [ 2] TYPE: S-STANDARD TS2 DETECTOR..... ECPI LOG..... NO DET PH - 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 EXTEND TIME... 0.0 DELAY TIME... 3.0

ENSURE DELAY

IS SET TO '3.0' USE ADDED INITIAL . CROSS SWITCH PH.. O LOCK IN..... NONE NTCIP VOL . OR OCC . PMT QUEUE DELAY. NO

- Place cursor in VEH DETECTOR [ ] position and enter "22". - Set assigned phase to "0".

VEH DETECTOR [22] VEH DET PLAN [ 2] TYPE: S-STANDARD TS2 DETECTOR..... ECPI LOG..... NO DET PH - 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 EXTEND TIME... O.O DELAY TIME... O.O USE ADDED INITIAL . CROSS SWITCH PH.. O LOCK IN..... NONE NTCIP VOL . OR OCC . PMT QUEUE DELAY. NO

END PROGRAMMING

U-4405 SIG-79.

PROJECT REFERENCE NO.

#### ALTERNATE PHASING ACTIVATION DETAIL

TO RUN ALT. PHASING DURING FREE RUN - PROGRAM CHANGES (SHOWN BELOW) IN A TIME BASED ACTION PLAN. SCHEDULE A DAY PLAN THAT INCLUDES THE ACTION PLAN PROGRAMMED TO SELECT VEH DET PLAN 2 AND ENABLE SF BIT 5.

TO RUN ALT. PHASING DURING COORDINATION - SELECT THE TIME BASED ACTION PLAN THAT IS PROGRAMMED TO SELECT VEH DET PLAN 2 AND ENABLE SF BIT 5.

| PHAS I NG                                 | VEH DET PLAN | SF BITS ENABLED |

|-------------------------------------------|--------------|-----------------|

| ACTIONS REQUIRED TO RUN DEFAULT PHASING   | 1            | NONE            |

| ACTIONS REQUIRED TO RUN ALTERNATE PHASING | 2            | 5               |

|                                           |              |                 |

IMPORTANT: IF ALT, PHASING IS USED DURING FREE RUN AND COORDINATION, DO NOT OPERATE TIME OF DAY EVENTS CONCURRENTLY WITH COORDINATION PLAN EVENTS IN THE EVENT SCHEDULER. (EX. FREE RUN EVENT SHOULD END BEFORE COORDINATION PLAN EVENT STARTS AND VICE-VERSA).

#### ALTERNATE PHASING CHANGE SUMMARY

THE FOLLOWING IS A SUMMARY OF WHAT TAKES PLACE WHEN SF BIT 5 AND VEH DET PLAN 2 ACTIVATE TO CALL THE "ALTERNATE PHASING":

SF BIT 5:

Modifies overlap parent phases for head 51 to run protected

Disables phase 2 call on loop 5A VEH DET PLAN 2: and reduces delay time for phase 5 call on loop 5A to 3 seconds.

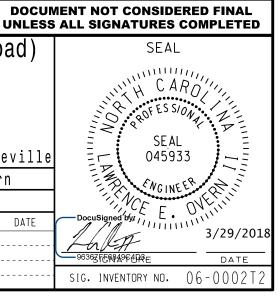

> THIS ELECTRICAL DETAIL IS FOR THE SIGNAL DESIGN: 06-0002T2 DESIGNED: March 2018 SEALED: 03-29-2018 REVISED: N/A

Temporary Design 2 - TMP Phase II

Electrical Detail - Sheet 2 of 2

Stantec

Stantec Consulting Services Inc.

Raleigh, NC 27606

Tel. (919) 851-6866

Fax. (919) 851-7024

www.stantec.com License No. F-0672

801 Jones Franklin Road-Suite 300

ELECTRICAL AND PROGRAMMING US 401 Bus./SR 1414 (Raeford Road) Prepared in the Offices of: PLAN DATE:

US 401 Bus. (Robeson Street) /McPhee Drive

Division 6 Cumberland County Fayetteville March 2018 REVIEWED BY: L Overn PREPARED BY: G B Spell REVIEWED BY:

REVISIONS INIT. DATE